티스토리 뷰

안녕하세요! 오늘은 반도체 업계와 금융 투자 시장을 뜨겁게 달구고 있는 삼성전자의 최신 기술 소식을 전해드리려고 합니다. 최근 국제고체회로학회(ISSCC 2026) 등에서 집중적으로 조명받은 삼성전자의 차세대 메모리 기술, 바로 '4F2 D램' 프로토타입에 대한 이야기입니다. 기존의 물리적 한계를 뛰어넘는 이 혁신적인 기술이 과연 무엇인지, 그리고 앞으로 반도체 시장에 어떤 변화를 가져올지 알기 쉽게 정리해 보았습니다.

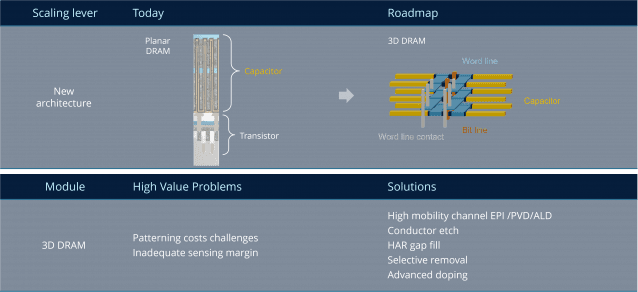

기존 6F2 구조의 물리적 한계를 부수다

우리가 현재 널리 사용하는 범용 D램은 트랜지스터의 주요 구성 요소(소스, 게이트, 드레인)가 웨이퍼 표면에 가로로 평평하게 눕혀진 '6F2' 구조를 취하고 있습니다. 하지만 반도체 미세 공정이 10나노미터 이하의 극한으로 접어들면서, 이 평면 구조로는 셀 크기를 더 이상 줄이기 힘든 뼈아픈 한계에 직면하게 되었습니다.

이러한 문제를 단번에 해결하기 위해 삼성전자가 꺼내든 카드가 바로 4F2 D램입니다. 핵심은 평면으로 누워있던 트랜지스터를 위아래로 꼿꼿하게 세우는 '수직형 채널 트랜지스터(VCT)' 구조입니다. 이렇게 건물을 위로 쌓아 올리듯 구조를 바꾸면 기존 대비 셀이 차지하는 면적을 30% 이상 획기적으로 줄일 수 있어, 아주 좁은 공간에도 엄청난 양의 데이터를 저장할 수 있게 됩니다.

초정밀 접합 기술, 하이브리드 카퍼 본딩(HCB)

이번 프로토타입에서 가장 눈길을 끄는 제조 공정은 서로 다른 웨이퍼를 직접 하나로 결합하는 '하이브리드 카퍼 본딩(HCB)' 기술입니다.

삼성전자는 데이터를 저장하는 '메모리 셀 어레이' 웨이퍼와 이를 구동하는 '주변부 로직 회로' 웨이퍼를 각각 따로 만들어냅니다. 그런 다음 이 두 웨이퍼를 HCB 기술을 이용해 위아래로 포개어 완벽하게 붙이는 구조를 선보였습니다. 놀랍게도 이때 두 웨이퍼를 이어주는 접합 간격(피치)은 약 300나노미터 수준에 불과합니다. 기존 낸드플래시나 HBM에 쓰이던 간격보다 훨씬 미세하고 정교한 초정밀 기술이 적용된 것입니다.

생산성 20% 증가와 강력한 파운드리 시너지

면적을 많이 차지하던 로직 회로를 메모리 셀 바로 밑바닥으로 숨기면서 공간 활용도가 극대화되었습니다. 그 결과 기존 6F2 구조와 비교했을 때 웨이퍼 한 장에서 뽑아낼 수 있는 반도체 칩(다이)의 출하량이 무려 20% 이상 증가하는 뛰어난 경제성을 입증했습니다.

무엇보다 이 기술은 전 세계에서 유일하게 메모리와 파운드리(반도체 위탁생산) 사업을 동시에 쥐고 있는 삼성전자만의 독보적인 무기가 될 전망입니다. 고도의 연산이 필요한 아래쪽 로직 회로는 첨단 파운드리 공정으로 찍어내고, 위쪽의 메모리 셀은 기존 메모리 공정으로 생산해 합치는 환상의 시너지를 발휘할 수 있기 때문입니다.

완전한 3D D램 시대를 향한 발판

업계 전문가들은 이 4F2 D램을 기반으로 한 칩 구조가 2027년경부터 본격적으로 시장에 도입될 것으로 내다보고 있습니다. 이번 프로토타입 공개는 평면 중심이었던 D램을 입체로 탈바꿈시키는 성공적인 첫걸음입니다. 앞으로 낸드플래시처럼 아파트 형태로 셀을 겹겹이 쌓아 올리는 '완전한 3D D램' 시대를 여는 결정적인 교두보가 될 것으로 기대됩니다.

#삼성전자 #4F2D램 #반도체 #차세대메모리 #하이브리드본딩 #HCB #파운드리 #3DD램 #프로토타입 #기술혁신

'IT 과학 테크' 카테고리의 다른 글

| 영국 자율주행 스타트업 '웨이브(Wayve)', 엔비디아·우버 등에서 1조 6천억 원 투자 유치! (0) | 2026.02.25 |

|---|---|

| 글로벌 빅테크의 인도 AI 시장 쟁탈전! 무료 선언 뒤에 숨은 진짜 목적은? (0) | 2026.02.25 |

| 우주의 숨겨진 역사를 다시 쓰다: 제임스 웹과 ALMA가 찾아낸 고대 먼지 은하 (1) | 2026.02.23 |

| 캘리포니아 공대(Caltech), 실리콘 칩에 광섬유급 성능 구현하는 획기적 기술 개발! 가시광선 영역 초저손실 달성 (0) | 2026.02.23 |

| 작은 물방울이 만든 푸른 에너지 혁명, 스위스 EPFL '블루 에너지' 돌파구 열다 (0) | 2026.02.20 |

- Total

- Today

- Yesterday

- 건강관리

- 테크뉴스

- 메타

- 지역경제

- 건강정보

- 국내여행

- 재테크

- 생활꿀팁

- IT뉴스

- K푸드

- 기후위기

- 청년정책

- 짧은뉴스

- 2026수능

- 경제뉴스

- 엔비디아

- 폭염주의보

- 가을축제

- 인공지능

- 상생페이백

- 정부지원금

- 쿠팡파트너스

- 삼성전자

- 전통시장

- 도시계획

- 티스토리블로그

- 생활정보

- 연말정산

- 탄소중립

- 미래기술

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |